IDE for e language SystemVerilog Verilog Verilog-AMS and VHDL. 1 4 bit Addition op.

Execute was to design a 1-bit ALU and then combine four of them to create a 4-bit ALU.

. N-bit Adder Design in Verilog. Last time I introduced the N-bit adder design in Verilog which is a part of a 16-bit ALU design I will present todayThe 16-bit ALU is a core combinational component of the processing unit in the coprocessor I introduced in the previous post. Design methodology has been changing from schematic design to HDL based design.

Adapted from this image. Professor 1 Sri Venkateswara Engineering College. Ad Hardware design verification for Verilog VHDL e Language or SystemVerilog.

In this Video you will learn how to design or implement the 4 bit ALU in verilog using Xilinx Simulator in very simple waySee Code here httpwww2dixco. Ac89774 on Mar 29 2017. It needs to be done in next 24 hours.

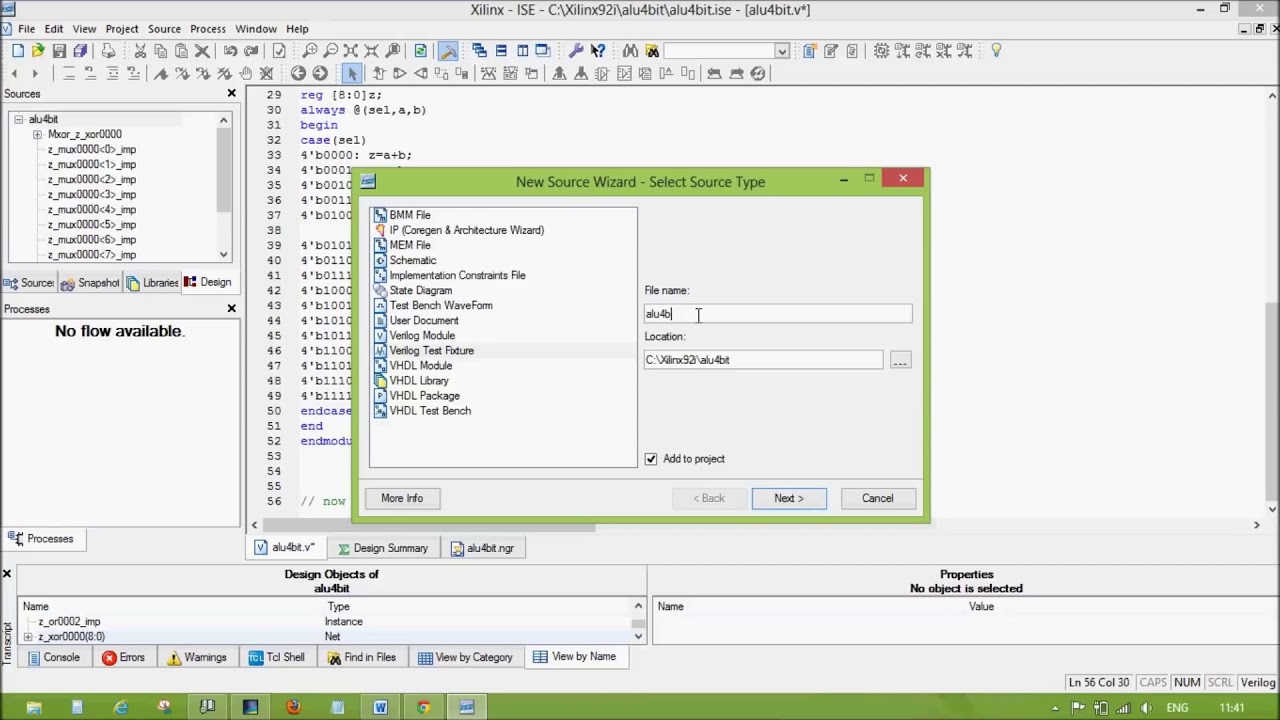

SRINATH 12631A0496 Under the Guidance of S. For this tutorial we have Xilinx ISE 144. Ive created and tested the code for a 1-bit Half Adder a 1-bit Full Adder a 4-bit Ripple Adder and 2s complement coding.

I want to create a 4 bit ALU that can add and divide and do other operation using Xilinx ISE design suite 147. This video describes the complete simulation flow step by step for VHDL Code using Xilinx ISE Design Suite 147 It helps beginners to understand the working. A full adder made by using two half adders and an OR gate.

Code 100 6 1s Complement of B op. This paper presents design concept of 4-bit arithmetic and logic unit ALU. Digital Clock manager DCM in Xilinx FPGA.

Functional Description of 4-bit Arithmetic Logic Unit. Each module of ALU is divided into smaller modules. So we will cheat and use a 4008 4-bit adder IC.

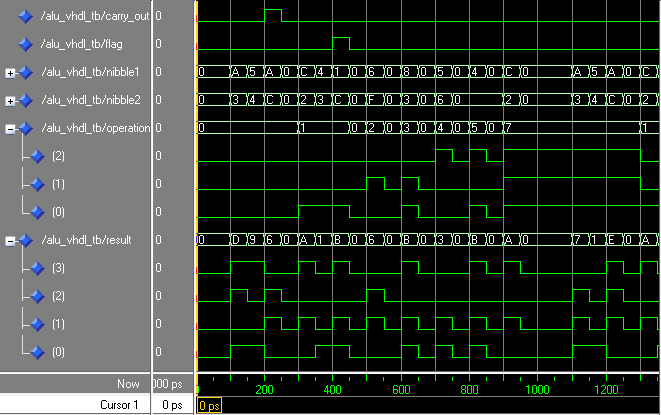

Mihir Gajjar and Mihir Gajjar 4 - bit ALU using Verilog. Since the output of the 4-bit ALU F30 is dependant on the signal M we have two ways of displaying our results. Full VHDL code for the ALU was presented.

Include addition subtraction and shifting We proposed arithmetic and logic unit using VHDL structural and dataflow level design. 4 bit ALU Design in verilog using Xilinx. Department of Electronics and Communication Engineering Athihrii Stephen Sanjay 2016 Page 19 Design and implementation of 32-bit ALU using Verilog 2016 Fig34 Arithmetic Logic Unit 32.

DESIGN AND SIMULATION OF DIFFERENT 8-BIT MULTIPLIERS USING VERILOG CODE BY P. 4008 4-bit full adder pinout. All the modules in arithmetic and.

This paper presents design concept of 4-bit arithmetic and logic unit ALU. Make sure you have installed Xilinx ISE 144 or later. Request a free demo.

Verilog code for Arithmetic Logic Unit ALU Last time an Arithmetic Logic Unit ALU is designed and implemented in VHDL. Im struggling with the code to make a 4-bit ALU in Verilog. Code 011 5 4 input NOR operation using dynamic NOR gate op.

Controlled by the three function select inputs sel 2 to 0 ALU can perform all the 8 possible logic operations. We proposed arithmetic and logic unit using VHDL structural and dataflow level design. In this tutorial we will walk you through the steps on how you can simulate a Verilog program in Xilinx Project Navigator.

There are 6 different functions implemented in this ALU. Unfortunately for the 4-bit ALU it would be impractical to use discrete chips to create a 4-bit adder. Follow the below-mentioned procedure to simulate your first Verilog program.

On the other hand when M1 the. Click to share on Twitter Opens in new window. RTL design starting from designing a top level RTL module for 4-bit ALU using hardware description language VHDL.

Code 000 2 2s Complement of A op. Code 010 4 4 input NAND operation using static NAND gate op. 4 - bit ALU using Verilog.

Today fpga4student presents the Verilog code for the ALU. Table of 32-bit Arithmetic Logic Unit 31. The testbench Verilog code for the ALU is also provided for simulation.

For shifter unit the selection line S1 is used to select either left or right shift micro-operation. Verilog VHDL FPGA Microcontroller Engineering. When M0 and the result from the 4-bit ALU is Logic based the result is displayed on an array of LEDs.

Jan 20 2018 - Verilog code for Multiplexers. SAIKIRAN 12631A0469 MSOUJANYA 12631A0488 SVEERANNA 12631A04A7 N. Simulation Result for 4-bit ALU.

Please inbox me further details. Verification of the designed RTL code using simulation techniques synthesis of RTL code to obtain gate level netlist using Xilinx ISE tool and Arithmetic Logic Unit was successfully designed and. PHP Software Architecture Verilog VHDL.

Full VHDL code for 16-bit ALU together with testbench will be presented in this VHDL project. Design methodology has been changing from schematic design to HDL based design. If you are interested please let me know so i can provide more details.

You can pick these up for a few dollars on eBay. Each module of ALU is divided into smaller modules. Code 001 3 4 bit Add-traction op.

Open 3264-bit Project Navigator. This project needs Xilinx for coding for hardware modeling and design and implementation of 4 bit ALU.

Lesson 60 Example 36 4 Bit Arithmetic Logic Unit Alu Youtube

Vhdl For Fpga Design 4 Bit Alu Wikibooks Open Books For An Open World

Verilog Code For Arithmetic Logic Unit Alu Fpga4student Com

0 comments

Post a Comment